By Joseph Gentile and Anna Shugol, IBM Poughkeepsie z/OS Performance Team

The last decade has seen a veritable explosion of data, driven by new technologies such as mobile transactions, social media, and the Internet of Things. Nowadays, it is not uncommon for a medium-sized company to process petabytes of data on a weekly basis. While scaling storage subsystems or archiving the data is not the most cost-effective solution, the mainframe platform provides an elegant solution to the data sprawl: on-host compression. Host-based zEnterprise Data Compression (zEDC) helps clients slow data growth and save DASD on z/OS. Similarly, clients have realized CPU and elapsed time savings with zEDC on encryption, batch, and network workloads. The new IBM z15 Integrated Accelerator for zEDC takes compression to the next level, introducing a new paradigm: Pervasive Compression. This article explores what the Integrated Accelerator for zEDC really is, how it works, and how you can take advantage of it.

Host-based compression was introduced to the mainframe platform in the late ‘90s with a z/Architecture instruction, CMPSC, and later with zEDC Express PCIe I/O cards. The design of host-based compression provides transparent exploitation by applications and middleware.

The mainframe platform offers several ways to leverage zEDC:

- Storage compression (BSAM/QSAM, SMF logstreams, DFHSM)

- Data transfer compression (IBM Sterling Connect:Direct)

- Storage compression for databases (Db2 LOBs, Db2 Archive logs)

- In-application compression – Java, zlib, hlasm

- Significant ISV usage

Benchmark results have proven the efficiency of zEDC Express compression, showing significant elapsed and CPU time benefits for I/O intensive workloads (using zEDC Express cards vs. uncompressed extended format data sets), and there was a wide adoption of the cards among mainframe customers. However, there were limitations:

- One zEDC Express card could only be shared between 15 LPARs, with at least four recommended to ensure high availability

- A maximum of 16 zEDC Express cards could be installed on a z14

With the new Integrated Accelerator for zEDC, this and other constraints have been lifted.

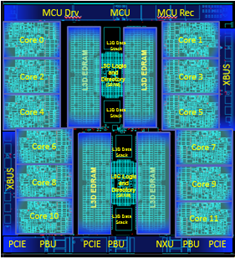

The Integrated Accelerator for zEDC is a new co-processor unit on the z15 processor chip, and is essentially a compression engine. The accelerator is shared between all 12 processor cores on a z15 processor chip (Figure 1). The cores share data with the accelerator using L3 cache, making data fetch very fast, and allowing very high compression bandwidth. The largest z15 with the Integrated Accelerator for zEDC provides up to 17 times the total compression throughput of a z14 configured with the maximum number of zEDC Express cards. The accelerator can be driven natively by any problem-state application through the DFLTCC instruction, which will run synchronously with respect to the invoking program. IBM Java 8 on z/OS has been updated to support synchronous execution of the Integrated Accelerator for zEDC. The java.util.zip.Deflater class on IBM Java 8 SR6 can achieve up to a 15x throughput improvement on z15 over IBM Java 8 SR5 FP25 on z14 with zEDC Express card, and the java.util.zip.GZIPOutputStream class can achieve up to a 2x improvement.

Figure 1: The z15 Processor Single Chip Module with Integrated Accelerator for zEDC (NXU in lower right corner)

The Integrated Accelerator for zEDC also maintains the same asynchronous model as the zEDC Express card, which is transparently called by DFSMS Access Methods when requested (via authorized APIs). The compression request is still forwarded to the I/O subsystem, where it is handled by a System Assist Processor (SAP). However, instead of shipping the request off to a zEDC Express card, it now invokes DFLTCC on the SAP. This avoids DFLTCC processing on General Processor CPUs, yet the data remains close to the processor, yielding an up to 8x application elapsed time speedup vs. the zEDC Express card, with no additional CPU time. The workload I/O interrupt cadence remains the same, which means that on z15, zEDC compression workloads will not suddenly prevent concurrent jobs from accessing the processor.

This design also means that no additional hardware or software configuration changes are required to exploit the Integrated Accelerator for zEDC when migrating from zEDC Express on z14 or earlier mainframes. On-chip compression complements the mainframe RAS (Reliability, Availability, and Serviceability) strategy, removing the I/O physical devices and eliminating a potential single point of failure. Backward compatibility to zEDC Express protects customer investments in compression: developers can use compression functions the same as they did on previous mainframe platforms. z/TPF can also exploit the accelerator; previously, it only offered software compression, which used up to 280x the CPU. Further, z/VM customers can exploit synchronous on-chip compression on z15 as well.

The Integrated Accelerator for zEDC introduced with z15 enables storage, CPU, and elapsed time savings, lowering the costs associated with data processing and transfer, while maintaining high performance and throughput. If your company is already a zEDC Express customer, the Integrated Accelerator for zEDC on the z15 can turn up compression performance to a new level. If your company does not yet exploit zEDC Express compression, the z15 offering provides several enticing benefits to your enterprise workloads.

Trademarks

IBM z14 is a trademark of IBM Corporation in the United States, other countries, or both.

Express, z/Architecture, z/VM are registered trademarks of IBM Corporation in the United States, other countries, or both.

Java is a trademark of Oracle and/or its affiliates in the United States, other countries, or both.

Connect:Direct is a registered trademark of IBM International Group B.V., an IBM Company in the U.S. and other countries.

Other company, product, and service names may be trademarks or service marks of others.